博通釋出3.5D XDSiP晶片封裝:6000平方毫米龐然巨物

鳳凰數碼 2024-12-10 01:38:30 1

快科技12月8日訊息,博通釋出了全新打造的3.5D XDSiP封裝平臺,專門面向超高效能的AI、HPC處理器,最高支援6000平方毫米的晶片面積。

這相當於大約八顆NVIDIA Blackwell架構的下一代旗艦晶片GB202,後者面積為744平方毫米。

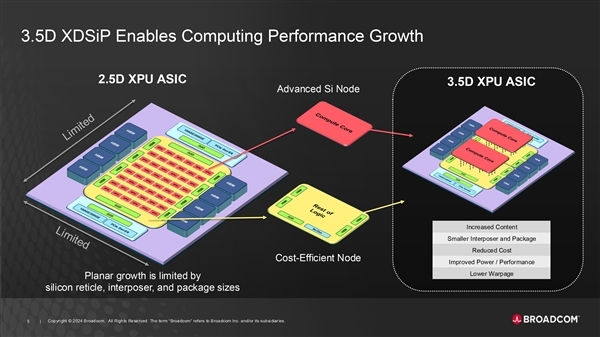

博通3.5D XDSiP使用了臺積電的CoWoS-L封裝技術,融合2.5D整合、3D封裝,所以叫3.5D。

它可以將3D堆疊晶片、網路與I/O芯粒、HBM記憶體整合在一起,構成系統級封裝(SiP),最大中介層面積4719平方毫米,大約相當於光罩面積的5.5倍,還可以封裝最多12顆HBM3或者HBM4高頻寬記憶體晶片。

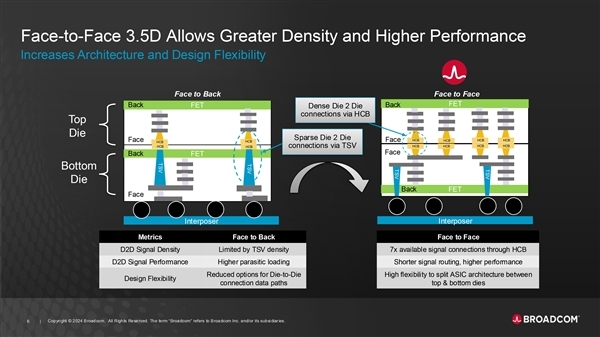

為了達成最高效能,博通建議分別設計不同的計算芯粒,然後採用F2F面對面的方法,藉助混合銅鍵合(HCB),將不同的芯粒堆疊在一起。

其中的關鍵在於使用無凸起HCB將上層Die與底層Die堆疊在一起,不再需要TSV矽通孔。

這麼做的好處非常多:訊號連線數量增加大約7倍,訊號走線更短,互連功耗降低最多90%,最大化降低延遲,堆疊更加靈活。

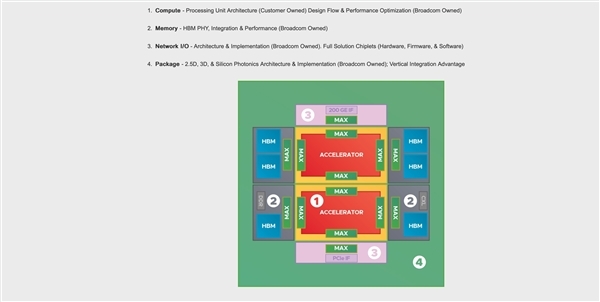

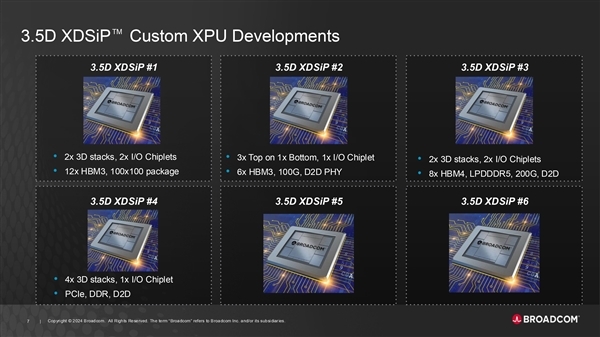

博通計劃利用3.5D XDSiP封裝為Google、Meta、OpenAI等設計定製化的AI/HPC處理器、ASIC晶片,並提供豐富的IP,包括HBM PHY、PCIe、GbE甚至是全套芯粒方案、矽光子技術。

這樣一來,客戶可以專心設計其處理器的最核心部分,即處理單元架構,無需考慮外圍IP和封裝。

博通預計首款產品將在2026年推出。

相關文章

- 蘋果取消最強晶片研發:改研究伺服器晶片

- 海貝R6PRO MAX便攜HIFI音樂播放器首銷:雙ES9039MS PRO晶片,6998元

- 349元學習神器!小米MIJIA詞典筆C1釋出:2600萬+英漢詞庫 沒網也能用

- 鎧俠釋出PCIe 5.0 SSD固態硬碟Exceria Plus G4,讀取最高10,000MB/s

- vivo Y300釋出:三向揚聲系統+6500mAh電池 1399元起

- 榮耀GT系列首款新品釋出:首發幻影引擎,售價2199元起

- 蔚來ET9先進數字架構正式釋出 將支援多品牌複用

- 美國晶片政策,將反噬

- 曝蘋果已取消史上最強M4 Extreme晶片!原定64核CPU、160核GPU

- AppGallery Awards 年度影響力應用與遊戲釋出,我們看到了鴻蒙應用生態的新趨勢