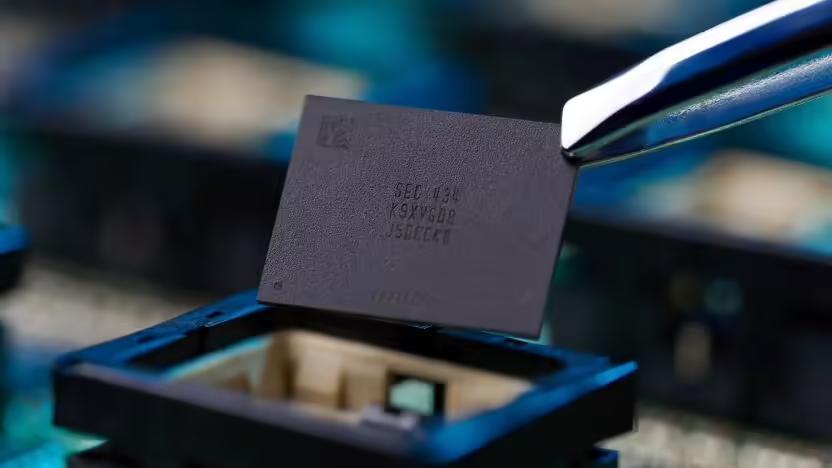

訊息稱三星下代400+層V-NAND 2026年推出,0a DRAM採用VCT結構

鳳凰數碼 2024-10-30 01:37:47 5

IT之家 10 月 29 日訊息,《韓國經濟日報》當地時間昨日表示,根據其掌握的最新三星半導體儲存路線圖,三星電子將於 2026 年推出的下代 V-NAND 堆疊層數超過 400,而預計於 2027 年推出的 0a nm DRAM 則將採用 VCT 結構。

三星目前最先進的 NAND 和 DRAM 工藝分別為第 9 代 V-NAND 和 1b nm(12 奈米級)DRAM。

報道表示三星第 10 代(即下代) V-NAND 將被命名為 BV(Bonding Vertical) NAND,這是因為這代產品將調整 NAND 結構,從目前的 CoP 外圍上單元改為分別製造儲存單元和外圍電路後垂直鍵合,整體思路與長江儲存 Xtacking、鎧俠-西部資料 CBA 相似。

韓媒表示,這一改動可防止 NAND 堆疊過程中對外圍電路結構的破壞,還能實現較 CoP 方案高出 60% 的位密度;2027 年的 V11 NAND 層數進一步增長,I/O 速率可提升 50%;未來有望實現千層堆疊。

而在 DRAM 記憶體領域,韓媒表示三星電子將於 2025 年上半年推出 1c nm DRAM,2026 年推出 1d nm DRAM,而到 2027 年則將推出第一代 10nm 以下級 0a nm DRAM 記憶體,整體同三星儲存器業務負責人李禎培此前展示的內容相近。

報道認為三星電子將在 0a nm 節點引入 VCT(IT之家注:垂直通道電晶體)技術,構建三維結構的 DRAM 記憶體,進一步提升容量的同時減少臨近單元干擾。此前訊息指,三星將於明年完成 4F2 VCT DRAM 原型開發。

相關文章

- 訊息稱餓了麼外賣正在上線新流量入口特團

- 萬元摺疊機皇!心繫天下三星W25正式釋出:售價15999元起

- 日產汽車:計劃到2026財年專門面向中國市場推出8款新能源車

- 史上最快警車?改裝廠商為特斯拉Model S Plaid推出警用套件

- 全新純電轎車諜照曝光:偽裝貼紙印“百萬級大沙發”,訊息稱系日產新車

- 分析稱廉價版Apple Vision頭顯將推遲至2027年後推出

- 古爾曼:Vision Pro將升級晶片,蘋果還考慮推出與iPhone連線的眼鏡

- VAIO推出勝色、全黑特別版SX14-R輕薄本,可選暗刻鍵帽

- 蘋果新版Vision Pro將於2025年推出:搭載M5晶片

- 訊息稱馬斯克正與英偉達就xAI投資事宜進行談判