AMD銳龍9 9950X3D處理器被曝單、多執行緒跑分與非X3D款接近

鳳凰數碼 2024-12-26 01:38:51 2

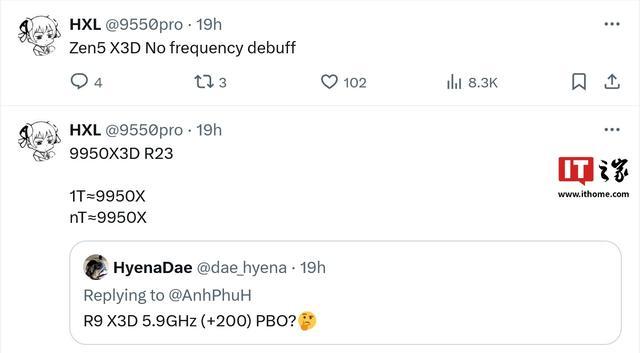

IT之家 12 月 24 日訊息,X 平臺使用者 HXL (@9550pro) 北京時間昨日表示,AMD 即將於 CES 2025 釋出的銳龍 9 9950X3D 處理器在 Cinebench R23 基準測試中多執行緒與單執行緒的成績均將與無 3D V-Cache 設計的 "Zen 5" 架構 16 核型號銳龍 9 9950X 大致相當。

這位訊息人士進一步表示,X3D 系列 "Zen 5" 處理器在頻率方面不會較非 X3D 款式出現下降。

IT之家注:

作為參考,AMD 銳龍 9 9950X 預設 TDP 為 170W,基準頻率為 4.3 GHz,加速頻率最高可達 5.7 GHz;而 12 核 24 執行緒的銳龍 9 9900X 處理器預設 TDP 同為 170W,基準頻率為 4.4 GHz,加速頻率最高可達 5.6 GHz。

參考此前爆料,雙 CCD 結構的銳龍 9 9900X3D / 9950X3D 處理器預計仍採用一顆大 L3 快取 CCD 搭配一顆高頻 CCD 的“不對稱”設計。

AMD 現已推出 8 核的銳龍 7 9800X3D 處理器,該 CPU 預設 TDP 為 120W,基準頻率為 4.7 GHz,加速頻率最高可達 5.2 GHz;其大致對應的非 X3D 型號銳龍 7 9700X 預設 TDP 是更低的 65W,基準頻率為 3.8 GHz,加速頻率最高可達 5.5 GHz。

從 AMD 官方分享的銳龍 7 9800X3D 處理器結構圖片上來看,AMD 在 "Zen 5" X3D 處理器上採用了 CCD 計算晶片在上、3D V-Cache 在下的新立體設計,這一改動有利於 CCD 散熱,進而提升了處理器的頻率上限。該結構預計也將用在銳龍 9 9950X3D 等款式上。

相關文章

- CBA最新排名:5隊爭第1白熱化 廣東全力衝刺 上海接近季後賽

- AMD銳龍9 9950X3D處理器被曝單、多執行緒跑分與非X3D款接近

- Overclock X5登場:MeLE首款45W處理器迷你電腦、雙網口,起價約2812元

- 三星Exynos處理器被曝迴歸!Galaxy S26系列有望搭載

- 銘凡推出新款MS-A1迷你工作站:處理器從R7 8700G升級為R9 9950X

- 賽昉科技釋出全新RISC-V處理器核心“昉・天樞-83”,效能超越Arm A75

- 天鋇預告新款AMD銳龍AI 9 HX 370處理器迷你主機,升級LPDDR5x-8000

- 一加平板標準版配置曝光:搭載天璣8350處理器、內建9520mAh電池

- GPD推出2025款Win 4掌上游戲電腦,搭載AMD Ryzen AI 9 HX 370處理器

- 安鈦克推出第二款掌機Core Micro,搭載聯發科G99處理器